# **NVIDIA A100 Tensor Core GPU Architecture**

**UNPRECEDENTED ACCELERATION AT EVERY SCALE**

# **Table of Contents**

| Introduction                                                                                                  | 7  |

|---------------------------------------------------------------------------------------------------------------|----|

| Introducing NVIDIA A100 Tensor Core GPU - our 8th Generation Data Center GPU for the Age of Elastic Computing | 9  |

| NVIDIA A100 Tensor Core GPU Overview                                                                          | 11 |

| Next-generation Data Center and Cloud GPU                                                                     | 11 |

| Industry-leading Performance for AI, HPC, and Data Analytics                                                  | 12 |

| A100 GPU Key Features Summary                                                                                 | 14 |

| A100 GPU Streaming Multiprocessor (SM)                                                                        | 15 |

| 40 GB HBM2 and 40 MB L2 Cache                                                                                 | 16 |

| Multi-Instance GPU (MIG)                                                                                      | 16 |

| Third-Generation NVLink                                                                                       | 16 |

| Support for NVIDIA Magnum IO™ and Mellanox Interconnect Solutions                                             | 17 |

| PCIe Gen 4 with SR-IOV                                                                                        | 17 |

| Improved Error and Fault Detection, Isolation, and Containment                                                | 17 |

| Asynchronous Copy                                                                                             | 17 |

| Asynchronous Barrier                                                                                          | 17 |

| Task Graph Acceleration                                                                                       | 18 |

| NVIDIA A100 Tensor Core GPU Architecture In-Depth                                                             | 19 |

| A100 SM Architecture                                                                                          | 20 |

| Third-Generation NVIDIA Tensor Core                                                                           | 23 |

| A100 Tensor Cores Boost Throughput                                                                            | 24 |

| A100 Tensor Cores Support All DL Data Types                                                                   | 26 |

| A100 Tensor Cores Accelerate HPC                                                                              | 28 |

| Mixed Precision Tensor Cores for HPC                                                                          | 28 |

| A100 Introduces Fine-Grained Structured Sparsity                                                              | 31 |

| Sparse Matrix Definition                                                                                      | 31 |

| Sparse Matrix Multiply-Accumulate (MMA) Operations                                                            | 32 |

| Combined L1 Data Cache and Shared Memory                                                                      | 33 |

| Simultaneous Execution of FP32 and INT32 Operations                                                           | 34 |

| A100 HBM2 and L2 Cache Memory Architectures                                                                   | 34 |

| A100 HBM2 DRAM Subsystem                                                         | 34 |

|----------------------------------------------------------------------------------|----|

| ECC Memory Resiliency                                                            | 35 |

| A100 L2 Cache                                                                    | 35 |

| Maximizing Tensor Core Performance and Efficiency for Deep Learning Applications | 38 |

| Strong Scaling Deep Learning Performance                                         | 38 |

| New NVIDIA Ampere Architecture Features Improved Tensor Core Performance         | 39 |

| Compute Capability                                                               | 44 |

| MIG (Multi-Instance GPU) Architecture                                            | 45 |

| Background                                                                       | 45 |

| MIG Capability of NVIDIA Ampere GPU Architecture                                 | 46 |

| Important Use Cases for MIG                                                      | 46 |

| MIG Architecture and GPU Instances in Detail                                     | 48 |

| Compute Instances                                                                | 50 |

| Compute Instances Enable Simultaneous Context Execution                          | 52 |

| MIG Migration                                                                    | 53 |

| Third-Generation NVLink                                                          | 53 |

| PCIe Gen 4 with SR-IOV                                                           | 54 |

| Error and Fault Detection, Isolation, and Containment                            | 54 |

| Additional A100 Architecture Features                                            | 55 |

| NVJPG Decode for DL Training                                                     | 55 |

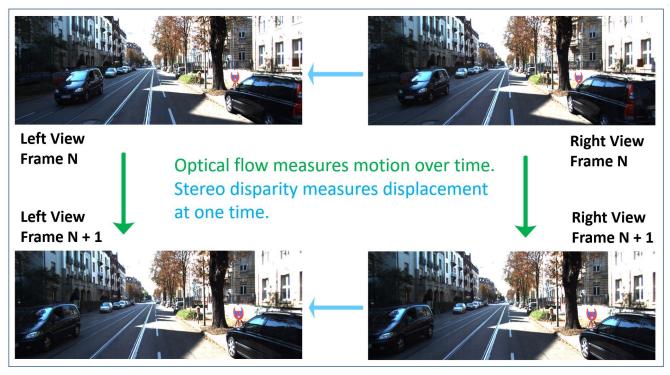

| Optical Flow Accelerator                                                         | 56 |

| Atomics Improvements                                                             | 57 |

| NVDEC for DL                                                                     | 57 |

| CUDA Advances for NVIDIA Ampere Architecture GPUs                                | 59 |

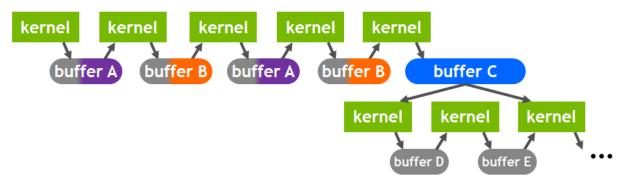

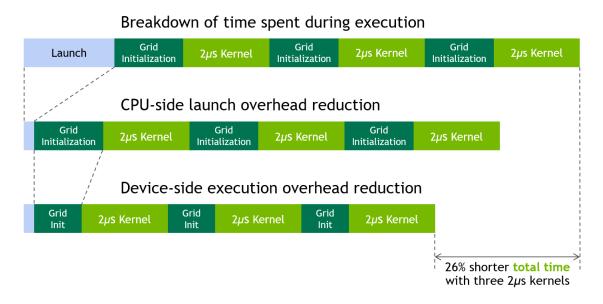

| CUDA Task Graph Acceleration                                                     | 59 |

| CUDA Task Graph Basics                                                           | 59 |

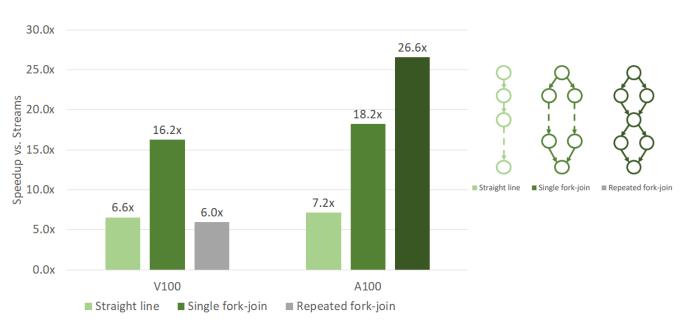

| Task Graph Acceleration on NVIDIA Ampere Architecture GPUs                       | 60 |

| CUDA Asynchronous Copy Operation                                                 | 62 |

| Asynchronous Barriers                                                            | 64 |

| L2 Cache Residency Control                                                       | 65 |

| Cooperative Groups                                                               | 67 |

| Conclusion                                                                       | 69 |

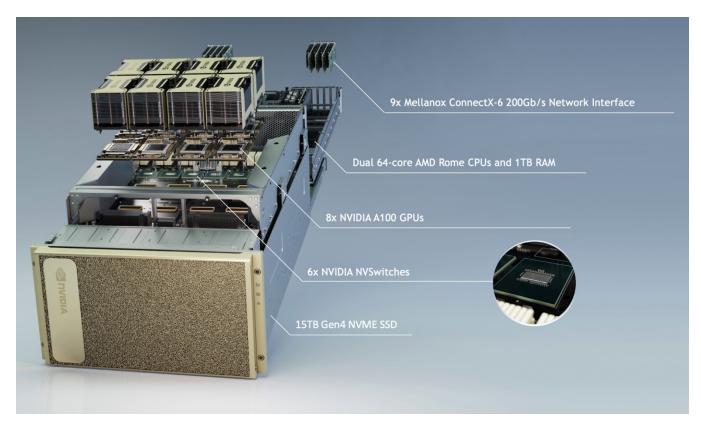

| Appendix A - NVIDIA DGX A100                                                     | 70 |

|                                                                                  |    |

| NVIDIA DGX A100 - The Universal System for Al Infrastructure | 70 |

|--------------------------------------------------------------|----|

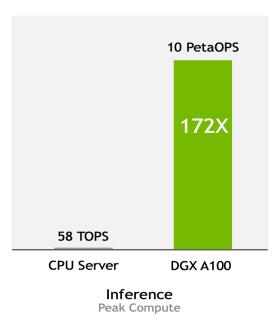

| Game-changing Performance                                    | 71 |

| Unmatched Data Center Scalability                            | 72 |

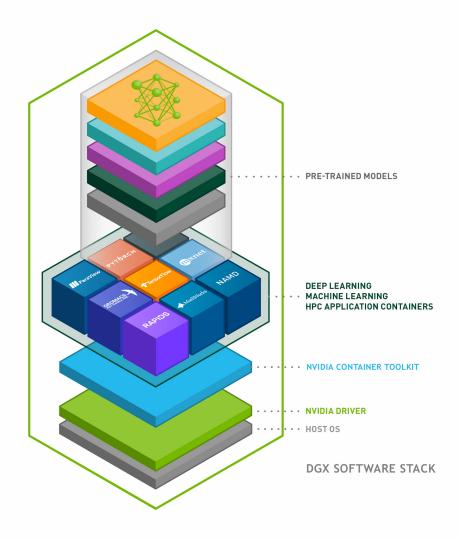

| Fully Optimized DGX Software Stack                           | 72 |

| NVIDIA DGX A100 System Specifications                        | 75 |

| Appendix B - Sparse Neural Network Primer                    | 77 |

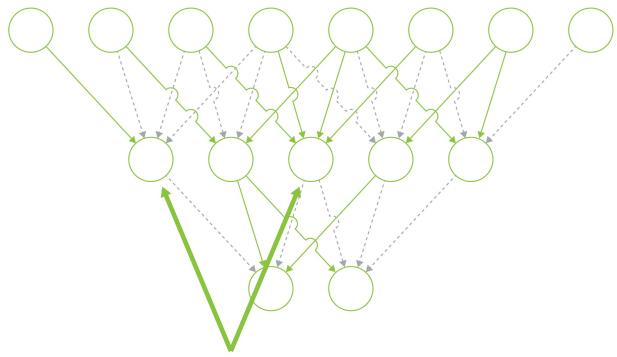

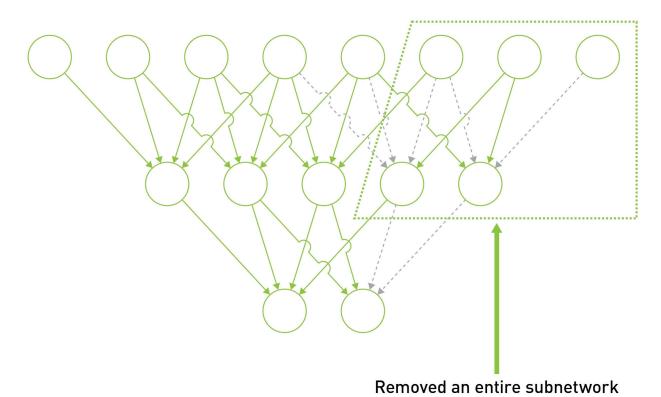

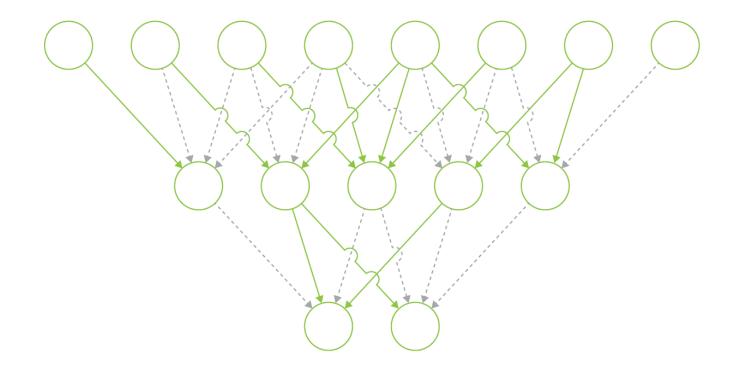

| Pruning and Sparsity                                         | 78 |

| Fine-Grained and Coarse-Grained Sparsity                     | 78 |

# List of Figures

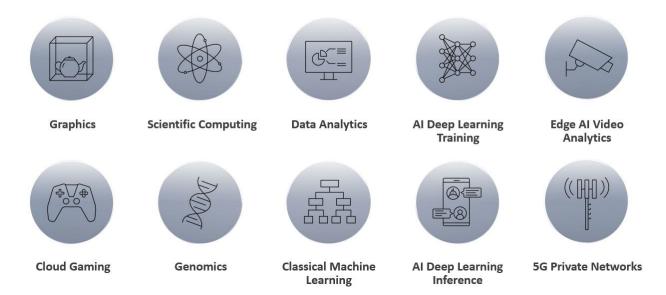

| Figure 1.  | Modern cloud datacenter workloads require NVIDIA GPU acceleration         | 8    |

|------------|---------------------------------------------------------------------------|------|

| Figure 2.  | New Technologies in NVIDIA A100                                           | . 10 |

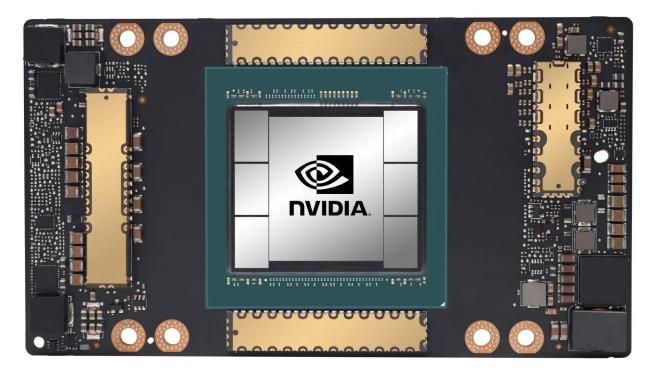

| Figure 3.  | NVIDIA A100 GPU on new SXM4 Module                                        | . 12 |

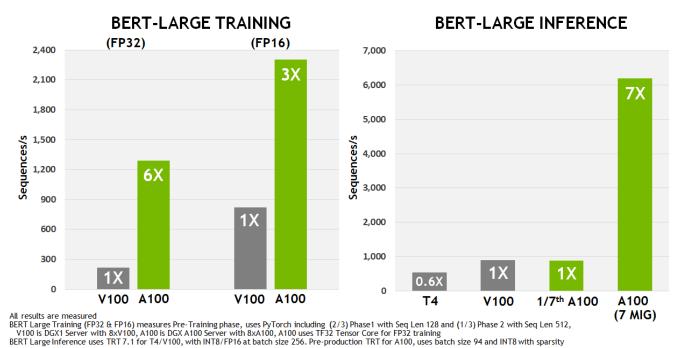

| Figure 4.  | Unified Al Acceleration for BERT-LARGE Training and Inference             | . 13 |

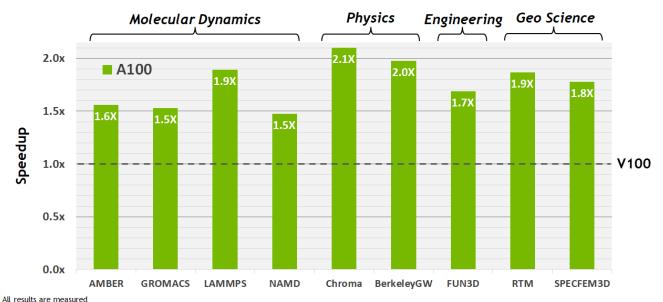

| Figure 5.  | A100 GPU HPC application speedups compared to NVIDIA Tesla V100           | . 14 |

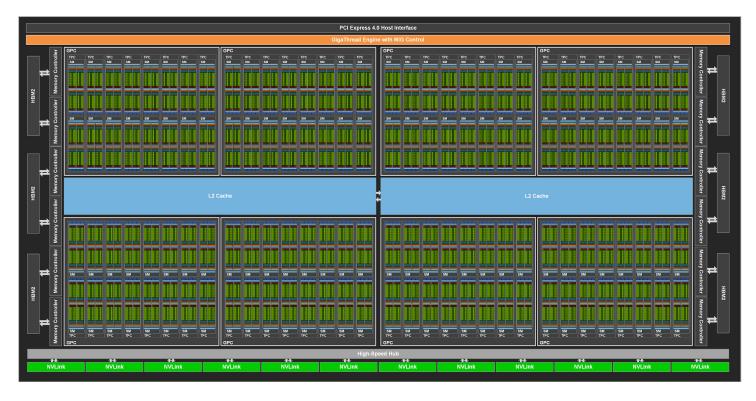

| Figure 6.  | GA100 Full GPU with 128 SMs (A100 Tensor Core GPU has 108 SMs)            | . 20 |

| Figure 7.  | GA100 Streaming Multiprocessor (SM)                                       | . 22 |

| Figure 8.  | A100 vs V100 Tensor Core Operations                                       | . 25 |

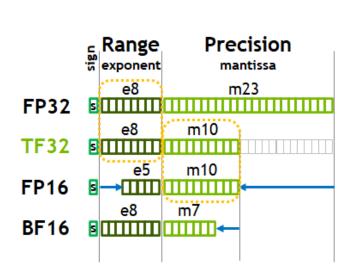

| Figure 9.  | TensorFloat-32 (TF32)                                                     | . 27 |

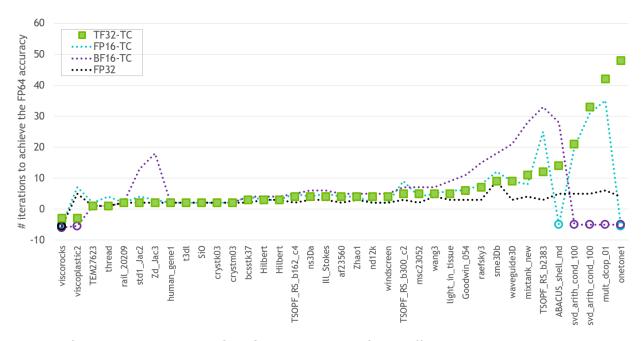

| Figure 10. | Iterations of TCAIRS Solver to Converge to FP64 Accuracy                  | . 30 |

| Figure 11. | TCAIRS solver speedup over the baseline FP64 direct solver                | . 30 |

| Figure 12. | A100 Fine-Grained Structured Sparsity                                     | . 32 |

| Figure 13. | Example Dense MMA and Sparse MMA operations                               | . 33 |

| Figure 14. |                                                                           |      |

| Figure 15. | A100 SM Data Movement Efficiency                                          | . 41 |

| Figure 16. | A100 L2 cache residency controls                                          | .42  |

| Figure 17. | A100 Compute Data Compression                                             | .42  |

| Figure 18. | A100 strong-scaling innovations                                           | .43  |

| Figure 19. | Software-based MPS in Pascal vs Hardware-Accelerated MPS in Volta         | . 45 |

| Figure 20. | CSP Multi-user node Today                                                 | . 47 |

| Figure 21. | Example CSP MIG Configuration                                             | .48  |

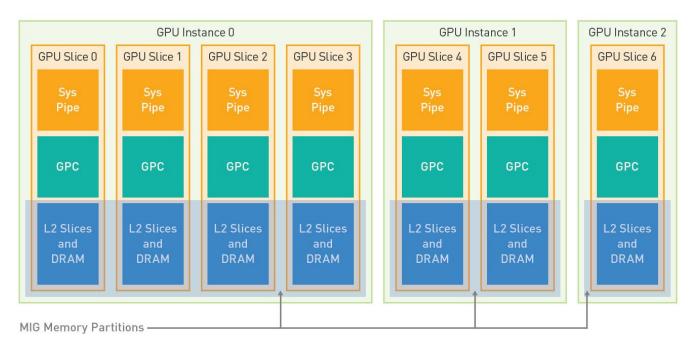

| Figure 22. | Example MIG compute configuration with three GPU Instances                | . 49 |

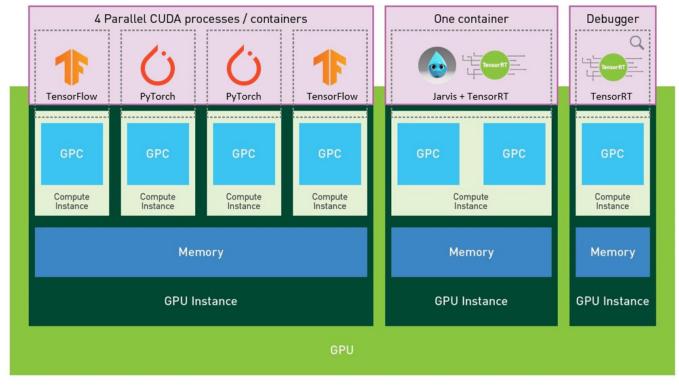

| Figure 23. | MIG Configuration with multiple independent GPU Compute workloads         | . 50 |

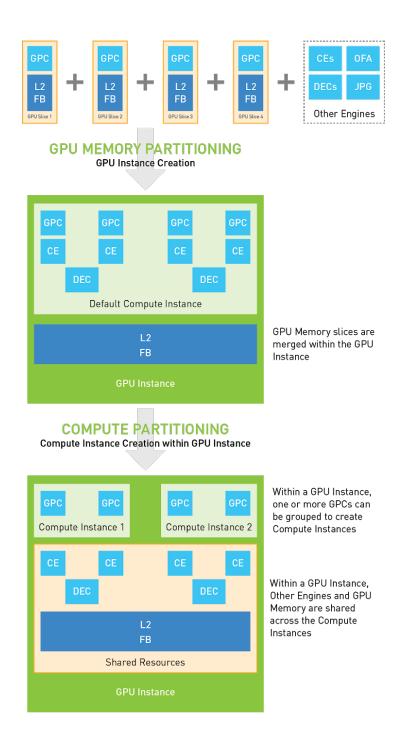

| Figure 24. | Example MIG partitioning process                                          | . 51 |

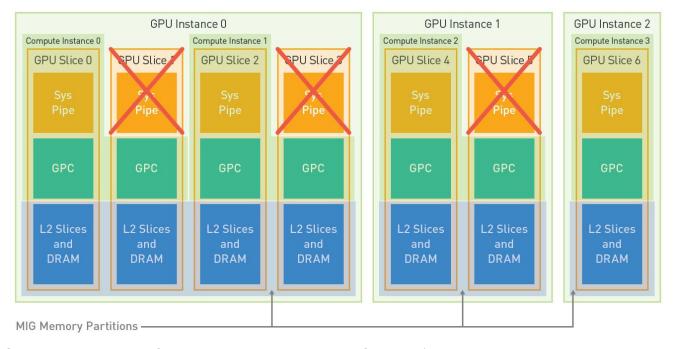

| Figure 25. | Example MIG config with three GPU Instances and four Compute Instances    | . 52 |

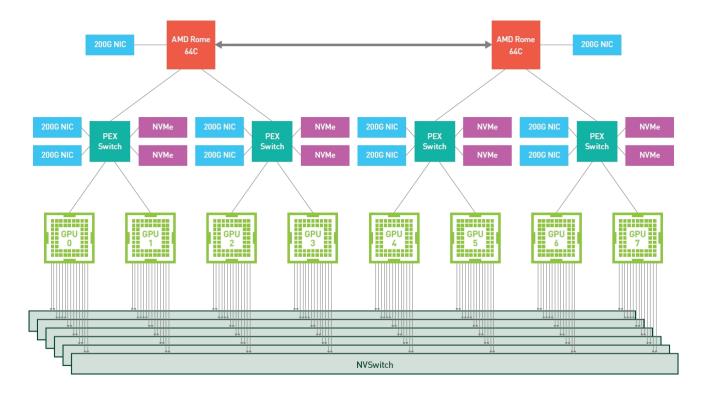

| Figure 26. | NVIDIA DGX A100 with Eight A100 GPUs                                      | . 54 |

| Figure 27. | Illustration of optical flow and stereo disparity                         | . 56 |

| Figure 28. | Execution Breakdown for Sequential 2us Kernels                            | . 60 |

| Figure 29. | Impact of Task Graph acceleration on CPU launch latency                   | . 61 |

| Figure 30. | Grid-to-Grid Latency Speedup using CUDA graphs                            | . 62 |

| Figure 31. | A100 Asynchronous Copy vs No Asynchronous Copy                            | . 63 |

| Figure 32. | Synchronous vs Asynchronous Copy to Shared Memory                         | . 64 |

| Figure 33. | A100 Asynchronous Barriers                                                | . 65 |

| Figure 34. | A100 L2 residency control example                                         | . 67 |

| Figure 35. | Warp-Wide Reduction                                                       | . 68 |

| Figure 36. | NVIDIA DGX 100 System                                                     | .70  |

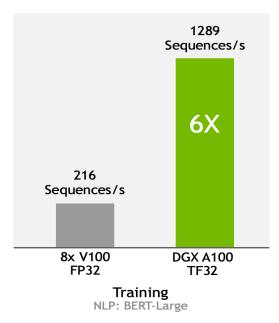

| Figure 37. | DGX A100 Delivers unprecedented AI performance for training and inference | . 71 |

| Figure 38. | NVIDIA DGX Software Stack                                                 | .73  |

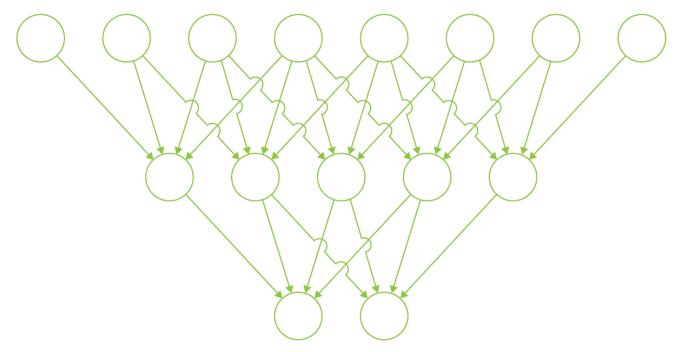

| Figure 39. | Dense Neural Network                                                      | .77  |

| Figure 40. | Fine-Grained Sparsity                                                     | . 79 |

| Figure 41. | Coarse Grained Sparsity                                                   | . 80 |

| Figure 42. | Fine Grained Structured Sparsity                                          | . 81 |

# **List of Tables**

| Table 1.  | NVIDIA A100 Tensor Core GPU Performance Specs                                 | 15   |

|-----------|-------------------------------------------------------------------------------|------|

| Table 2.  | A100 speedup over V100 (TC=Tensor Core, GPUs at respective clock speeds)      | 23   |

| Table 3.  | A100 Tensor Core Input / Output Formats and Performance vs FP32 FFMA          | 27   |

| Table 4.  | Comparison of NVIDIA Data Center GPUs                                         | 37   |

| Table 5.  | Compute Capability: GP100 vs GV100 vs GA100                                   | 44   |

| Table 6.  | NVJPG Decode Rate at different video formats                                  | 56   |

| Table 7.  | GA100 HW decode support                                                       | 57   |

| Table 8.  | Decode performance @ GPU boost clock (1410 MHz)                               | 58   |

| Table 9.  | A100 vs V100 Decode Comparison @ 1080p30                                      | 58   |

| Table 10. | NVIDIA DGX A100 System Specifications                                         | 75   |

| Table 11. | Accuracy achieved on various networks with 2:4 fine grained structured sparsi | ty82 |

#### Introduction

The diversity of compute-intensive applications running in modern cloud data centers has driven the explosion of NVIDIA GPU-accelerated cloud computing. Such intensive applications include AI deep learning training and inference, data analytics, scientific computing, genomics, edge video analytics and 5G services, graphics rendering, cloud gaming, and many more. From scaling-up AI training and scientific computing, to scaling-out inference applications, to enabling real-time conversational AI, NVIDIA GPUs provide the necessary horsepower to accelerate numerous complex and unpredictable workloads running in today's cloud data centers.

NVIDIA® GPUs are the leading computational engines powering the AI revolution, providing tremendous speedups for AI training and inference workloads. In addition, NVIDIA GPUs accelerate many types of HPC and data analytics applications and systems, allowing customers to effectively analyze, visualize, and turn data into insights. NVIDIA's accelerated computing platforms are central to many of the world's most important and fastest-growing industries.

HPC has grown beyond supercomputers running computationally-intensive applications such as weather forecasting, oil & gas exploration, and financial modeling. Today, millions of NVIDIA GPUs are accelerating many types of HPC applications running in cloud data centers, servers, systems at the edge, and even deskside workstations, servicing hundreds of industries and scientific domains.

Al networks continue to grow in size, complexity, and diversity, and the usage of Al-based applications and services is rapidly expanding. NVIDIA GPUs accelerate numerous Al systems and applications including: deep learning recommendation systems, autonomous machines (self-driving cars, factory robots, etc.), natural language processing (conversational Al, real-time language translation, etc.), smart city video analytics, software-defined 5G networks (that can deliver Al-based services at the Edge), molecular simulations, drone control, medical image analysis, and more.

#### **DIVERSE WORKLOADS IN MODERN CLOUD COMPUTING**

Diverse and computationally-intensive workloads in modern cloud data centers require NVIDIA GPU acceleration

Figure 1. Modern cloud datacenter workloads require NVIDIA GPU acceleration

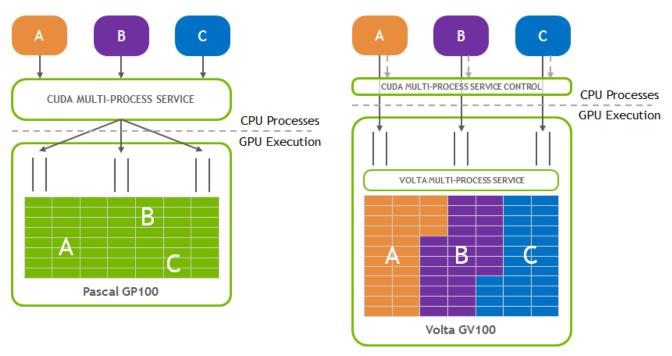

In 2017, the NVIDIA Tesla® V100 GPU introduced powerful new "Tensor Cores" that provided tremendous speedups for the matrix computations at the heart of deep learning neural network training and inferencing operations. In 2018, the NVIDIA Tesla® T4 GPU using NVIDIA Turing™ Tensor Cores and the Tensor RT™ inference optimizer and runtime brought significant speedups to data center inferencing with energy-efficient performance. Turing Tensor Cores also enabled amazing new Al capabilities in Turing GPU-based GeForce® gaming PCs and Quadro® workstations.

On the industry-standard MLPerf AI benchmark, NVIDIA Volta™ GPUs delivered winning results in the training categories, while Turing GPUs won the data center and edge categories in the recently introduced MLPerf inferencing benchmarks. NVIDIA Jetson AGX Xavier™ also delivered the best inferencing performance of all commercially available SoC devices.

For over a decade, the NVIDIA CUDA® development platform has unleashed the power of GPUs to accelerate a wide variety of application areas. Innovations and improvements in APIs, software stacks, libraries, and code optimizers are just as important as advancements in GPU hardware. The <a href="NVIDIA CUDA Toolkit">NVIDIA CUDA Toolkit</a>, provides numerous software tools for developers, including the <a href="NVIDIA CUDA-X™">NVIDIA CUDA-X™</a> GPU-accelerated libraries for AI, HPC, and data analytics. Also many containers for AI frameworks and HPC applications, including models and scripts, are available for free in the <a href="NVIDIA GPU Cloud™">NVIDIA GPU Cloud™</a> (NGC) to simplify programming and speed up

development and deployment of GPU-accelerated applications. <u>Kubernetes on NVIDIA GPUs</u> is also available for free to enable enterprises to seamlessly scale up and scale out training and inference deployments across multi-cloud GPU clusters.

# Introducing NVIDIA A100 Tensor Core GPU - our 8th Generation Data Center GPU for the Age of Elastic Computing

The new **NVIDIA® A100 Tensor Core GPU** builds upon the capabilities of the prior NVIDIA Tesla V100 GPU, adding many new features while delivering significantly faster performance for HPC, AI, and data analytics workloads. Powered by the NVIDIA Ampere architecture-based GA100 GPU, the A100 provides very strong scaling for GPU compute and deep learning applications running in single- and multi-GPU workstations, servers, clusters, cloud data centers, systems at the edge, and supercomputers. The A100 GPU enables building elastic, versatile, and high throughput data centers.

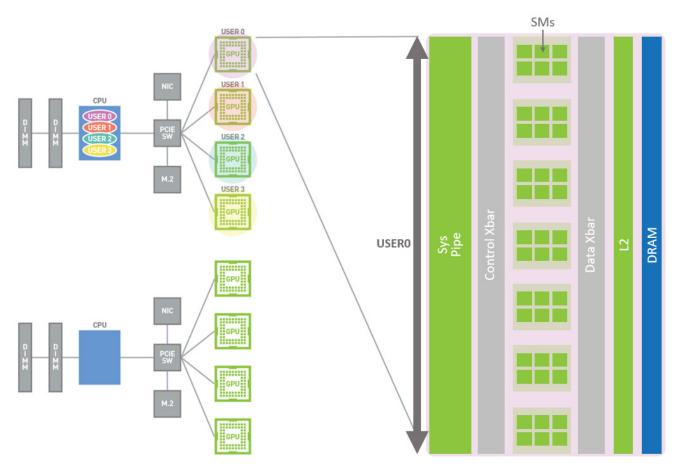

The A100 GPU includes a revolutionary new "**Multi-Instance GPU**" (or **MIG**) virtualization and GPU partitioning capability that is particularly beneficial to Cloud Service Providers (CSPs). When configured for MIG operation, the A100 permits CSPs to improve utilization rates of their GPU servers, delivering up to 7x more GPU Instances for no additional cost. Robust fault isolation allows customers to partition a single A100 GPU safely and securely.

A100 adds a powerful new Third-Generation Tensor Core that boosts throughput over V100 while adding comprehensive support for DL and HPC data types, together with a new Sparsity feature to deliver a further doubling of throughput.

New TensorFloat-32 (TF32) Tensor Core operations in A100 provide an easy path to accelerate FP32 input/output data in DL frameworks and HPC, running 10x faster than V100 FP32 FMA operations or 20x faster with sparsity. For FP16/FP32 mixed-precision DL, the A100 Tensor Core delivers 2.5x the performance of V100, increasing to 5x with sparsity.

New Bfloat16 (BF16)/FP32 mixed-precision Tensor Core operations run at the same rate as FP16/FP32 mixed-precision. Tensor Core acceleration of INT8, INT4, and binary round out support for DL inferencing, with A100 sparse INT8 running 20x faster than V100 INT8. For HPC, the A100 Tensor Core includes new IEEE-compliant FP64 processing that delivers 2.5x the FP64 performance of V100.

Figure 2. New Technologies in NVIDIA A100

The A100 GPU is designed for broad performance scalability. Customers can share a single A100 using MIG GPU partitioning technology, or use multiple A100 GPUs connected by the new Third-generation NVIDIA NVLink® high-speed interconnect in powerful new NVIDIA DGX™, NVIDIA HGX™, and NVIDIA EGX™ systems. A100-based systems connected by the new NVIDIA NVSwitch™ and Mellanox® state-of-the-art InfiniBand™ and Ethernet solutions can be scaled out to tens, hundreds, or thousands of A100s in compute clusters, cloud instances, or immense supercomputers to accelerate many types of applications and workloads. Additionally, the A100 GPU's revolutionary new hardware capabilities are enhanced by new CUDA 11 features that improve programmability and reduce AI and HPC software complexity.

The NVIDIA A100 GPU is the **first elastic GPU architecture** with the ability to scale-up to giant GPUs using NVLink, NVSwitch, and InfiniBand, or scale-out to support multiple independent users with MIG, simultaneously achieving great performance and lowest cost per-GPU instance.

The NVIDIA A100 Tensor Core GPU delivers the greatest generational leap in NVIDIA GPU accelerated computing ever.

#### **NVIDIA A100 Tensor Core GPU Overview**

#### Next-generation Data Center and Cloud GPU

Increasingly complex and varied AI, HPC, and data analytics workloads require additional GPU computing power, multi-GPU connectivity enhancements, and a comprehensive suite of supporting software stacks. NVIDIA meets these growing GPU computing challenges with the new NVIDIA A100 Tensor Core GPU based on the NVIDIA Ampere GPU architecture, combined with new CUDA software advances.

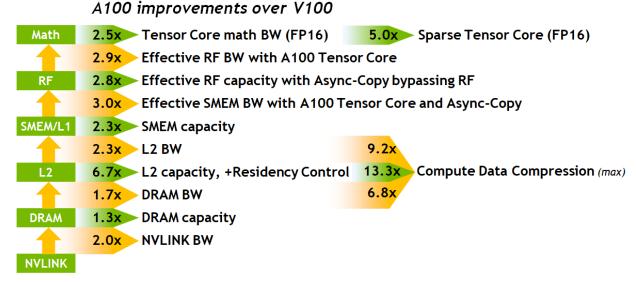

The A100 GPU includes many core architecture enhancements that deliver significant speed-ups for AI, HPC, and data analytics workloads compared to V100, as explained throughout this paper. The new **Sparsity** feature further accelerates math operations by up to 2x. High-bandwidth HBM2 memory and larger, faster caches feed data to the increased numbers of CUDA Cores and Tensor Cores.

The new Third-generation NVLink and PCIe Gen 4 speed up multi-GPU system configurations. Many other enhancements enable strong scaling for hyperscale data centers, and robust Multi-Instance GPU (MIG) virtualization for Cloud Service Provider (CSP) systems and their customers. NVIDIA Ampere architecture also improves ease of programming, while lowering latencies, and reducing Al and HPC software complexity. NVIDIA Ampere architecture GPUs deliver all these new features with greater performance per watt than the prior generation NVIDIA Volta GPUs.

The NVIDIA A100 GPU is architected to not only accelerate large complex workloads, but also efficiently accelerate many smaller workloads. A100 enables building data centers that can accommodate unpredictable workload demand, while providing fine-grained workload provisioning, higher GPU utilization, and improved TCO.

Figure 3. NVIDIA A100 GPU on new SXM4 Module

A100's versatility helps infrastructure managers maximize the utility of every GPU in their data center to meet different-sized performance needs, from the smallest job to the biggest multinode workload. A100 powers the NVIDIA data center platform that includes Mellanox HDR InfiniBand (IB), NVSwitch, HGX A100, and the Magnum IO SDK for scaling up. This integrated team of technologies efficiently scales to tens of thousands of GPUs to train the most complex AI networks at unprecedented speed.

Diffusing accelerated computing within enterprise and cloud environments demands high utilization on small workloads. With the new Multi-Instance GPU technology, each A100 can be divided into as many as seven GPU Instances for optimal utilization and to expand access to every user and application.

#### Industry-leading Performance for AI, HPC, and Data Analytics

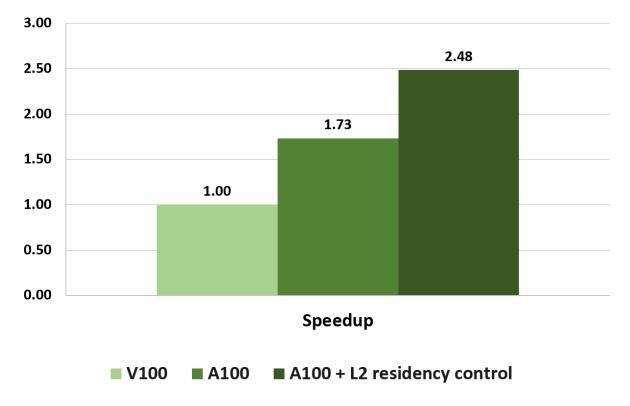

The NVIDIA A100 GPU delivers exceptional speedups over V100 for AI training and inference workloads as shown in Figure 4. Similarly, Figure 5 shows substantial performance improvements across different HPC applications.

### UNIFIED AI ACCELERATION

A100 GPU performance in BERT deep learning training and inference scenarios compared to NVIDIA Tesla V100 and NVIDIA Tesla T4.

Figure 4. Unified AI Acceleration for BERT-LARGE Training and Inference

#### **ACCELERATING HPC**

Au Tesutica are ineasured Except BerkeleyGW, V100 used is single V100 SXM2. A100 used is single A100 SXM4

More apps detail: AMBER based on PME-Cellulose, CROMACS with STMV (h-bond), LAMMPS with Atomic Fluid LJ-2.5, NAMD with v3.0a1 STMV\_NVE

Chroma with szscl21\_24\_128, FUN3D with dpw, RTM with Isotropic Radius 4 1024^3, SPECFEM3D with Cartesian four material model

BerkeleyGW based on Chi Sum and uses 8xV100 in DGX-1, vs 8xA100 in DGX A100

Figure 5. A100 GPU HPC application speedups compared to NVIDIA Tesla V100

#### A100 GPU Key Features Summary

The NVIDIA A100 Tensor Core GPU is the world's fastest cloud and data center GPU accelerator designed to power computationally-intensive AI, HPC, and data analytics applications.

Fabricated on TSMC's 7nm N7 manufacturing process, the NVIDIA Ampere architecture-based GA100 GPU that powers A100 includes **54.2** billion transistors with a die size of **826 mm2**.

A high-level summary of key A100 features is provided below for a quick understanding of the important new A100 technologies and performance levels. In-depth architecture information is presented in subsequent sections.

#### A100 GPU Streaming Multiprocessor (SM)

The new SM in the NVIDIA Ampere architecture-based A100 Tensor Core GPU significantly increases performance, builds upon features introduced in both the Volta and Turing SM architectures, and adds many new capabilities.

The A100 **Third-Generation Tensor Cores** enhance operand sharing and improve efficiency, and add powerful new data types including:

- TF32 Tensor Core instructions which accelerate processing of FP32 data

- IEEE-compliant FP64 Tensor Core instructions for HPC

- BF16 Tensor Core instructions at the same throughput as FP16

Table 1. NVIDIA A100 Tensor Core GPU Performance Specs

| Peak FP64 <sup>1</sup>             | 9.7 TFLOPS                           |

|------------------------------------|--------------------------------------|

| Peak FP64 Tensor Core <sup>1</sup> | 19.5 TFLOPS                          |

| Peak FP32 <sup>1</sup>             | 19.5 TFLOPS                          |

| Peak FP16 <sup>1</sup>             | 78 TFLOPS                            |

| Peak BF16 <sup>1</sup>             | 39 TFLOPS                            |

| Peak TF32 Tensor Core <sup>1</sup> | 156 TFLOPS   312 TFLOPS <sup>2</sup> |

| Peak FP16 Tensor Core <sup>1</sup> | 312 TFLOPS   624 TFLOPS <sup>2</sup> |

| Peak BF16 Tensor Core <sup>1</sup> | 312 TFLOPS   624 TFLOPS <sup>2</sup> |

| Peak INT8 Tensor Core <sup>1</sup> | 624 TOPS   1,248 TOPS <sup>2</sup>   |

| Peak INT4 Tensor Core <sup>1</sup> | 1,248 TOPS   2,496 TOPS <sup>2</sup> |

<sup>1 -</sup> Peak rates are based on GPU Boost Clock.

New **Sparsity** support in A100 Tensor Cores can exploit fine-grained structured sparsity in deep learning networks to double the throughput of Tensor Core operations. Sparsity features are described in detail in the "**A100 Introduces Fine-Grained Structured Sparsity**" section below.

The larger and faster L1 cache and shared memory unit in A100 provides 1.5x the aggregate capacity per SM compared to V100 (192 KB vs 128 KB per SM) to deliver additional acceleration for many HPC and AI workloads.

A number of other new SM features improve programmability and reduce software complexity.

<sup>2 -</sup> Effective TFLOPS / TOPS using the new Sparsity feature

#### 40 GB HBM2 and 40 MB L2 Cache

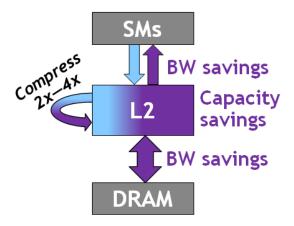

To feed its massive computational throughput, the NVIDIA A100 GPU has 40 GB of high-speed HBM2 memory with a class-leading 1555 GB/sec of memory bandwidth - a 73% increase compared to Tesla V100. In addition, the A100 GPU has significantly more on-chip memory including a 40 MB Level 2 (L2) cache - nearly 7x larger than V100 - to maximize compute performance. With a new partitioned crossbar structure, the A100 L2 cache provides 2.3x the L2 cache read bandwidth of V100.

To optimize capacity utilization, the NVIDIA Ampere architecture provides L2 cache residency controls for you to manage data to keep or evict from the cache. A100 also adds Compute Data Compression to deliver up to an additional 4x improvement in DRAM bandwidth and L2 bandwidth, and up to 2x improvement in L2 capacity.

#### Multi-Instance GPU (MIG)

The new Multi-Instance GPU (MIG) feature allows the A100 Tensor Core GPU to be securely partitioned into as many as seven separate GPU Instances for CUDA applications, providing multiple users with separate GPU resources to accelerate their applications and development projects.

With MIG, each instance's processors have separate and isolated paths through the entire memory system - the on-chip crossbar ports, L2 cache banks, memory controllers, and DRAM address busses are all assigned uniquely to an individual instance. This ensures that an individual user's workload can run with predictable throughput and latency, with the same L2 cache allocation and DRAM bandwidth, even if other tasks are thrashing their own caches or saturating their DRAM interfaces.

MIG increases GPU hardware utilization while providing a defined QoS and isolation between different clients (such as VMs, containers, and processes). MIG is especially beneficial for Cloud Service Providers who have multi-tenant use cases, and it ensures one client cannot impact the work or scheduling of other clients, in addition to providing enhanced security and allowing GPU utilization guarantees for customers.

#### Third-Generation NVLink

The third-generation of NVIDIA's high-speed NVLink interconnect implemented in A100 GPUs and the new NVSwitch significantly enhances multi-GPU scalability, performance, and reliability. With more links per GPU and switch, the new NVLink provides much higher GPU-GPU communication bandwidth, and improved error-detection and recovery features.

Third-generation NVLink has a data rate of 50 Gbit/sec per signal pair, nearly doubling the 25.78 Gbits/sec rate in V100. A single A100 NVLink provides 25 GB/second bandwidth in each direction similar to V100, but using only half the number of signal pairs per link compared to

V100. The total number of links is increased to twelve in A100, versus 6 in V100, yielding 600 GB/sec total bandwidth versus 300 GB/sec for V100.

#### Support for NVIDIA Magnum IO™ and Mellanox Interconnect Solutions

The NVIDIA A100 Tensor Core GPU is fully compatible with NVIDIA Magnum IO and Mellanox state-of-the-art InfiniBand and Ethernet interconnect solutions to accelerate multi-node connectivity. The NVIDIA Magnum IO APIs integrate computing, networking, file systems, and storage to maximize IO performance for multi-GPU, multi-node accelerated systems. It interfaces with CUDA-X™ libraries to accelerate IO across a broad range of workloads, from AI to data analytics to visualization.

#### PCIe Gen 4 with SR-IOV

The A100 GPU supports PCI Express Gen 4 (PCIe Gen 4) which doubles the bandwidth of PCIe 3.0/3.1 by providing 31.5 GB/sec versus 15.75 GB/sec for x16 connections. The faster speed is especially beneficial for A100 GPUs connecting to PCIe 4.0-capable CPUs, and to support fast network interfaces, such as 200 Gbit/sec InfiniBand. A100 also supports Single Root Input/Output Virtualization (SR-IOV), which allows sharing and virtualizing a single PCIe connection for multiple processes or Virtual Machines (VMs).

#### Improved Error and Fault Detection, Isolation, and Containment

It is critically important to maximize GPU uptime and availability by detecting, containing, and often correcting errors and faults, rather than forcing GPU resets, especially in large multi-GPU clusters and single-GPU, multi-tenant environments such as MIG configurations. The NVIDIA A100 Tensor Core GPU includes new technology to improve error/fault attribution, isolation, and containment as described in the in-depth architecture sections below.

#### Asynchronous Copy

The A100 GPU includes a new asynchronous copy instruction that loads data directly from global memory into SM shared memory, eliminating the need for intermediate register file (RF) usage. Async-copy reduces register file bandwidth, uses memory bandwidth more efficiently, and reduces power consumption. As the name implies, asynchronous copy can be done in the background while the SM is performing other computations.

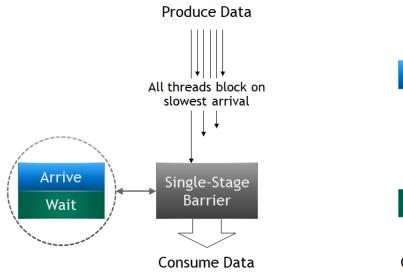

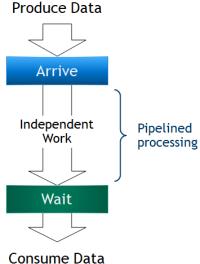

#### Asynchronous Barrier

The A100 GPU provides hardware-accelerated barriers in shared memory. These barriers are available using CUDA 11 in the form of ISO C++-conforming barrier objects. Asynchronous barriers split apart the barrier arrive and wait operations, and can be used to overlap asynchronous copies from global memory into shared memory with computations in the SM. They can be used to implement producer-consumer models using CUDA threads. Barriers also

provide mechanisms to synchronize CUDA threads at different granularities, not just warp or block level.

#### Task Graph Acceleration

CUDA Task Graphs provide a more efficient model for submitting work to the GPU. A task graph consists of a series of operations, such as memory copies and kernel launches, connected by dependencies. Task graphs enable a define-once/run-repeatedly execution flow. A predefined task graph allows the launch of any number of kernels in a single operation, greatly improving application efficiency and performance. A100 adds new hardware features to make the paths between grids in a task graph significantly faster.

## NVIDIA A100 Tensor Core GPU Architecture In-Depth

The NVIDIA A100 GPU based on NVIDIA Ampere architecture is engineered to provide as much AI and HPC computing power as possible from its many new architectural features and optimizations. A100 is built on the TSMC 7nm N7 FinFET fabrication process that provides higher transistor density, improved performance, and better power efficiency than the 12nm FFN process used in Tesla V100. A new Multi-Instance GPU (MIG) capability provides enhanced client/application fault isolation and QoS for multi-tenant and virtualized GPU environments which is especially beneficial to Cloud Service Providers. A faster and more error-resilient third-generation of NVIDIA's NVLink interconnect delivers improved multi-GPU performance scaling for hyperscale data centers.

The NVIDIA GA100 GPU is composed of multiple GPU Processing Clusters (GPCs), Texture Processing Clusters (TPCs), Streaming Multiprocessors (SMs), and HBM2 memory controllers.

The **full implementation** of the GA100 GPU includes the following units:

- 8 GPCs, 8 TPCs/GPC, 2 SMs/TPC, 16 SMs/GPC, 128 SMs per full GPU

- 64 FP32 CUDA Cores/SM, 8192 FP32 CUDA Cores per full GPU

- 4 Third-generation Tensor Cores/SM, 512 Third-generation Tensor Cores per full GPU

- 6 HBM2 stacks, 12 512-bit Memory Controllers

The **NVIDIA A100 Tensor Core GPU implementation** of the GA100 GPU includes the following units:

- 7 GPCs, 7 or 8 TPCs/GPC, 2 SMs/TPC, up to 16 SMs/GPC, 108 SMs

- 64 FP32 CUDA Cores/SM, 6912 FP32 CUDA Cores per GPU

- 4 Third-generation Tensor Cores/SM, 432 Third-generation Tensor Cores per GPU

- 5 HBM2 stacks, 10 512-bit Memory Controllers

The TSMC 7nm N7 process used to build the GA100 GPU allows many more GPCs, TPCs, and SM units, along with many other new hardware features in a die size similar to the Volta GV100 GPU (which was fabricated on TSMC's 12nm FFN process).

Figure 6 shows a full GA100 GPU with 128 SMs. The A100 is based on GA100 and has 108 SMs.

Figure 6. GA100 Full GPU with 128 SMs (A100 Tensor Core GPU has 108 SMs)

#### A100 SM Architecture

The new A100 SM significantly increases performance, builds upon features introduced in both the Volta and Turing SM architectures, and adds many new capabilities and enhancements.

The A100 SM diagram is shown in Figure 7. Volta and Turing have eight Tensor Cores per SM, with each Tensor Core performing 64 FP16/FP32 mixed-precision fused multiply-add (FMA) operations per clock. The A100 SM includes new third-generation Tensor Cores that each perform 256 FP16/FP32 FMA operations per clock. A100 has four Tensor Cores per SM, which together deliver 1024 dense FP16/FP32 FMA operations per clock, a 2x increase in computation horsepower per SM compared to Volta and Turing.

Key SM features are briefly highlighted below (and described in detail in subsequent sections):

- Third-generation Tensor Cores:

- Acceleration for all data types including FP16, BF16, TF32, FP64, INT8, INT4, and Binary.

- New Tensor Core sparsity feature exploits fine-grained structured sparsity in deep learning networks, doubling the performance of standard Tensor Core operations.

- TF32 Tensor Core operations in A100 provide an easy path to accelerate FP32 input/output data in DL frameworks and HPC, running 10x faster than V100 FP32 FMA operations, or 20x faster with sparsity.

- FP16/FP32 mixed-precision Tensor Core operations deliver unprecedented processing power for DL, running 2.5x faster than Tesla V100 Tensor Core operations, increasing to 5x with sparsity.

- BF16/FP32 mixed-precision Tensor Core operations run at the same rate as FP16/FP32 mixed-precision.

- FP64 Tensor Core operations deliver unprecedented double precision processing power for HPC, running 2.5x faster than V100 FP64 DFMA operations.

- INT8 Tensor Core operations with sparsity deliver unprecedented processing power for DL Inference, running up to 20x faster than V100 INT8 operations.

- 192 KB of combined shared memory and L1 data cache, 1.5x larger than V100 SM

- New asynchronous copy instruction loads data directly from global memory into shared memory, optionally bypassing L1 cache, and eliminating the need for intermediate register file (RF) usage

- New shared-memory-based barrier unit (asynchronous barriers) for use with the new asynchronous copy instruction

- New instructions for L2 cache management and residency controls

- New warp-level reduction instructions supported by CUDA Cooperative Groups

- Many programmability improvements which reduce software complexity

Figure 7. GA100 Streaming Multiprocessor (SM)

#### Third-Generation NVIDIA Tensor Core

Tensor Cores are specialized high-performance compute cores for matrix math operations that provide groundbreaking performance for AI and HPC applications. Tensor Cores perform matrix multiply and accumulate (MMA) calculations. Hundreds of Tensor Cores operating in parallel in one NVIDIA GPU enable massive increases in throughput and efficiency. Tensor Cores were first introduced in the NVIDIA Tesla V100 GPU, and further enhanced in NVIDIA's more recent Turing GPUs. (Refer to the <a href="NVIDIA Tesla V100 GPU Architecture">NVIDIA Tesla V100 GPU Architecture</a> for background information on Tensor Core operation.)

Table 2. A100 speedup over V100 (TC=Tensor Core, GPUs at respective clock speeds)

|                                 | V100        | A100        | A100<br>Sparsity <sup>1</sup> | A100<br>Speedup | A100 Speedup with Sparsity |

|---------------------------------|-------------|-------------|-------------------------------|-----------------|----------------------------|

| A100 FP16 vs<br>V100 FP16       | 31.4 TFLOPS | 78 TFLOPS   | NA                            | 2.5x            | NA                         |

| A100 FP16 TC vs<br>V100 FP16 TC | 125 TFLOPS  | 312 TFLOPS  | 624 TFLOPS                    | 2.5x            | 5x                         |

| A100 BF16 TC vs<br>V100 FP16 TC | 125 TFLOPS  | 312 TFLOPS  | 624 TFLOPS                    | 2.5x            | 5x                         |

| A100 FP32 vs<br>V100 FP32       | 15.7 TFLOPS | 19.5 TFLOPS | NA                            | 1.25x           | NA                         |

| A100 TF32 TC vs<br>V100 FP32    | 15.7 TFLOPS | 156 TFLOPS  | 312 TFLOPS                    | 10x             | 20x                        |

| A100 FP64 vs<br>V100 FP64       | 7.8 TFLOPS  | 9.7 TFLOPS  | NA                            | 1.25x           | NA                         |

| A100 FP64 TC vs<br>V100 FP64    | 7.8 TFLOPS  | 19.5 TFLOPS | NA                            | 2.5x            | NA                         |

| A100 INT8 TC vs<br>V100 INT8    | 62 TOPS     | 624 TOPS    | 1248 TOPS                     | 10x             | 20x                        |

| A100 INT4 TC                    | NA          | 1248 TOPS   | 2496 TOPS                     | NA              | NA                         |

| A100 Binary TC                  | NA          | 4992 TOPS   | NA                            | NA              | NA                         |

<sup>1 -</sup> Effective TOPS / TFLOPS using the new Sparsity Feature

#### A100 Tensor Cores Boost Throughput

The new third-generation Tensor Core architecture in A100 delivers double the raw dense Tensor throughput per SM compared to V100, accelerates more data types, and delivers tremendous additional 2x speedups for sparse matrix computations.

General Matrix-Matrix Multiplication (GEMM) operations are at the core of neural network training and inference, and are used to multiply large matrices of input data and weights in various layers. The GEMM operation computes the matrix product D = A \* B + C, where C and D are m-by-n matrices, A is an m-by-k matrix, and B is a k-by-n matrix. The problem size of such GEMM operations running on Tensor Cores is defined by the matrix sizes, and typically denoted as m-by-n-by-k.

Using FP16/FP32 mixed-precision Tensor Core operations as an example, at the hardware level, each Tensor Core in the Volta architecture can execute 64 FP16 fused multiply-add operations (FMAs) with FP32 accumulation per clock, allowing it to compute a mixed-precision 4x4x4 matrix multiplication per clock. Since each Volta SM includes eight Tensor Cores, a single SM delivers 512 FP16 FMA operations per clock or 1024 individual FP16 floating point operations per clock. Each of the A100 Tensor Cores can execute 256 FP16 FMA operations per clock, allowing it to compute the results for an 8x4x8 mixed-precision matrix multiplication per clock. Each SM in the A100 GPU includes four of the new redesigned Tensor Cores and therefore each SM in A100 delivers 1024 FP16 FMA operations per clock (or 2048 individual FP16 floating point operations per clock).

Comparing total GPU performance, not just SM-level performance, the NVIDIA A100 Tensor Core GPU with its 108 SMs includes a total of 432 Tensor Cores that deliver up to 312 TFLOPS of dense mixed-precision FP16/FP32 performance. That equates to 2.5x the mixed-precision Tensor Core performance of the entire Tesla V100 GPU, and 20x V100's standard FP32 (FMA operations running on traditional FP32 CUDA cores) throughput.

Figure 8 compares V100 and A100 FP16 Tensor Core operations, and also compares V100 FP32, FP64, and INT8 standard operations to respective A100 TF32, FP64, and INT8 Tensor Core operations. Throughputs are aggregate per GPU, with A100 using sparse Tensor Core operations for FP16, TF32, and INT8. Note the upper left diagram shows two V100 FP16 Tensor Cores, since a V100 SM has two Tensor Cores per SM partition, while an A100 SM one.

A100 Tensor Core operations compared to V100 Tensor Core and standard operations for different data types.

Figure 8. A100 vs V100 Tensor Core Operations

#### A100 Tensor Cores Support All DL Data Types

In addition to FP16 precision introduced on the Volta Tensor Core, and the INT8, INT4 and binary 1-bit precisions added in the Turing Tensor Core, the A100 Tensor Core adds support for TF32, BF16 and FP64 formats. (FP64 double-precision MMA is discussed in the next section).

Volta GPU architecture introduced Tensor Cores that operate on IEEE FP16 data types, providing 8x more math throughput compared to V100 FP32. Results are accumulated into FP32 for mixed precision training or FP16 for inference. From a raw architectural performance perspective, if both A100 and V100 were operating at the same clock speed, a single A100 SM delivers 2x FP16 Tensor Core performance compared to the V100 SM, and 16x compared to standard V100 (and A100) FP32 FFMA operations.

Turing architecture extended Tensor Cores to handle more inference use cases by adding INT8, INT4, and Binary support. On Turing these provided 16x, 32x, and 128x more math throughput when compared to FP32. The A100 SM delivers 2x INT8, INT4, and Binary Tensor Core performance compared to the Turing SM, respectively, and 32x, 64x, and 256x compared to A100 FP32 FFMA.

NVIDIA Ampere architecture adds three additional formats to Tensor Cores – BF16, TF32 and FP64. BF16 is an alternative to IEEE FP16, and includes an 8-bit exponent, 7-bit mantissa, and 1 sign-bit. Both FP16 and BF16 have been shown to successfully train neural networks in mixed-precision mode, matching FP32 training results without hyper-parameter adjustment. Both FP16 and BF16 modes of Tensor Cores provide 16x more math throughput than FP32 in A100 GPUs.

Today, the default math for AI training is FP32, without tensor core acceleration. The NVIDIA Ampere architecture introduces new support for TF32, enabling AI training to use tensor cores by default with no effort on the user's part. Non-tensor operations continue to use the FP32 datapath, while TF32 tensor cores read FP32 data and use the same range as FP32 with reduced internal precision, before producing a standard IEEE FP32 output. TF32 includes an 8-bit exponent (same as FP32), 10-bit mantissa (same precision as FP16) and 1 sign-bit.

As with Volta, Automatic Mixed Precision (AMP) enables users to use mixed precision with FP16 for AI training with just a few lines of code changes. Using AMP, A100 delivers a further 2X faster Tensor Core performance over TF32.

TensorFloat-32 (TF32) provides the range of FP32 with the precision of FP16, 8x precision vs. BF16 (left). A100 accelerates tensor math with TF32 while supporting FP32 input and output data (right), enabling easy integration into DL and HPC programs and automatic acceleration of DL frameworks.

Figure 9. TensorFloat-32 (TF32)

Table 3. A100 Tensor Core Input / Output Formats and Performance vs FP32 FFMA.

|      | INPL    | IT OPERANDS | AC    | CUMULATOR | TOPS | X-factor<br>vs. FFMA | SPARSE<br>TOPS | SPARSE<br>X-factor<br>vs. FFMA |

|------|---------|-------------|-------|-----------|------|----------------------|----------------|--------------------------------|

| V400 | FP32    |             | FP32  |           | 15.7 | 1x                   | -              | -                              |

| V100 | FP16    | <u></u>     | FP32  |           | 125  | 8x                   | -              | -                              |

|      | FP32    | ((IIIII)    | FP32  |           | 19.5 | 1x                   | -              | -                              |

|      | TF32    | [[[[[]]]]]  | FP32  |           | 156  | 8x                   | 312            | 16x                            |

|      | FP16    | (IIII)      | FP32  |           | 312  | 16x                  | 624            | 32x                            |

|      | BF16    |             | FP32  |           | 312  | 16x                  | 624            | 32x                            |

| A100 | FP16    | 0000        | FP16  |           | 312  | 16x                  | 624            | 32x                            |

|      | INT8    |             | INT32 |           | 624  | 32x                  | 1248           | 64x                            |

|      | INT4    | <b></b>     | INT32 |           | 1248 | 64x                  | 2496           | 128x                           |

|      | BINARY  | 0           | INT32 |           | 4992 | 256x                 | -              | -                              |

|      | IEEE FF | 964 <b></b> |       |           | 19.5 | 1x                   | -              | -                              |

**Note:** TOPS column indicates TFLOPS for floating-point ops and TOPS for integer ops. X-factors compare MMA ops with and without sparsity to standard FP32 FFMA ops. (Sparse TOPS represents effective TOPS / TFLOPS using the new Sparsity feature.)

To summarize the user choices for NVIDIA Ampere architecture math for Deep Learning training:

- By default, TF32 tensor cores are used, with no adjustment to user scripts. Up to 8x more throughput compared to FP32 on A100 and up to 10x compared to FP32 on V100.

- FP16 or BF16 mixed-precision training should be used for maximum training speed. Up to 2x more throughput compared to TF32, and up to 16x compared to FP32 on A100 and up to 20x compared to FP32 on V100.

#### A100 Tensor Cores Accelerate HPC

The performance needs of High-Performance Computing (HPC) applications are growing rapidly. Many applications from a wide range of scientific and research disciplines rely on double precision (FP64) computations. To meet the rapidly growing compute needs of HPC computing, A100 Tensor Cores support acceleration of IEEE-compliant FP64 computations, delivering up to 2.5x the FP64 performance of the NVIDIA Tesla V100 GPU. The new Double Precision Matrix Multiply Add instruction on A100 replaces 8 DFMA instructions on V100, reducing instruction fetches, scheduling overhead, register reads, datapath power, and shared memory read bandwidth. Using Tensor Cores, each SM in A100 computes a total of 64 FP64 FMA operations/clock (or 128 FP64 operations/clock), which is twice the throughput of Tesla V100. The A100 Tensor Core GPU with 108 SMs delivers a peak FP64 throughput of 19.5 TFLOPS, which is 2.5x that of Tesla V100.

With support for these new formats, the A100 Tensor Cores can be used to accelerate HPC workloads, iterative solvers, and various new Al algorithms.

#### Mixed Precision Tensor Cores for HPC

One of the most promising applications for mixed-precision Tensor Cores in HPC is the field of iterative refinement methods. Iterative refinement methods are commonly used for solving linear systems of equations, which occur ubiquitously in HPC applications in a wide range of fields such as earth science, fluid dynamics, healthcare, material science, and nuclear energy, as well as oil and gas exploration.

The Tensor Core Accelerated Iterative Refinement Solver (TCAIRS) in cuSOLVER automates usage of mixed precision for this application. Last year, a fusion reaction study for the International Thermonuclear Experimental Reactor demonstrated that mixed-precision techniques delivered a speedup of 3.5x on V100 for such solvers using V100's FP16 Tensor Cores. The same technology used in that study tripled the Summit supercomputer's performance on the HPL-Al benchmark.

cuSOLVER in CUDA 11.0 adds support for A100's new tensor core formats including TF32. Figure 10 and Figure 11 below show results of the TCAIRS solver on 37 tests from the SuiteSparse Matrix collection, comparing convergence rate and performance for FP32, FP16 with input scaling, BF16, and TF32. These were compared to the performance of the reference FP64 solver which leverages the FP64 Tensor Cores on the A100. In cases where the mixed-

precision solver automatically falls back to the FP64 solver due to slow or no convergence, the number of iterations were recorded as negative, and speedup is less than one, as it included the cost of the failed attempt.

As shown in Figure 10 and Figure 11, TF32 delivered the fastest and most robust results compared to other Tensor Core modes. The number of iterations to converge was the lowest for TF32 amongst the Tensor Core modes. While FP32 had one fallback case, TF32 had only two, compared to three for FP16 with input scaling, and six for BF16 Tensor Core modes. The geomean speedup over the FP64 solver was 2.0X for TF32 Tensor Cores compared to 1.9X for FP16 and 1.8X for BF16. For large matrices with a size of around 40K with complex numbers, the TCAIRS solver delivers speedups of up to 4X with TF32 on A100.

The applications of mixed-precision Tensor Core acceleration are not limited to dense linear solvers, and can be extended to sparse problems, in addition to other numerical methods where matrix multiplies represent a significant portion of the algorithmic complexity.

Number of iterations taken by the TCAIRS solver compared for 37 different problems to converge to FP64 accuracy for different precisions. The results are sorted by increasing number of iterations for TF32. Negative figures indicate the solver did not converge with reduced precision and fell back to a full FP64 solution.

4.0 —■—TF32-TC 3.5 ..... FP16-TC •••• BF16-TC Speedup of TCAIRS over FP64 3.0 •••• FP32 2.5 1.0 ö ö ö 0.5 0.0 sme3Db Zd\_Jac3 ns3Da t3dl af23560 Zhao1 svd\_arith\_cond\_100 thread nd12k waveguide3D Hilbert viscorocks mult\_dcop\_01 rail 20209 TSOPF RS b300 c2 mixtank\_new crystm03 svd\_arith\_cond\_100 light\_in\_tissue viscoplastic2 onetone1 FSOPF\_RS\_b162\_c4 std1\_Jac2 human\_gene1 raefsky3 bcsstk37 III\_Stokes Goodwin\_054 msc23052 TEM27623 crystk03 TSOPF\_RS\_b2383 ABACUS\_shell\_md Hilbert windscreen

Figure 10. Iterations of TCAIRS Solver to Converge to FP64 Accuracy

Speedup of the TCAIRS solver over the baseline FP64 direct solver compared for 37 different problems. Cases where speedups are less than one indicate that the TCAIRS solver did not converge with reduced precision and fell back to a full FP64 solution. The results are sorted by increasing speedup for TF32.

Figure 11. TCAIRS solver speedup over the baseline FP64 direct solver

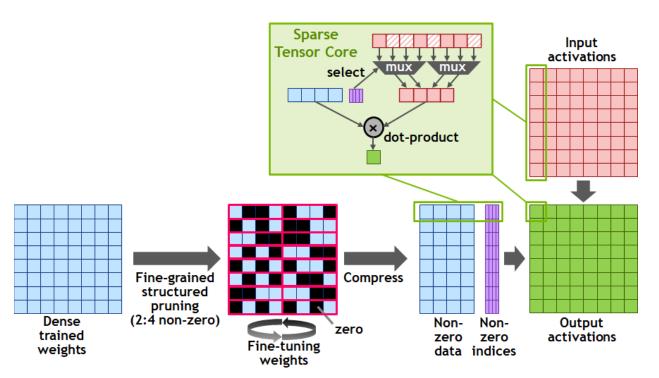

#### A100 Introduces Fine-Grained Structured Sparsity

With the A100 GPU, NVIDIA introduces Fine-Grained Structured Sparsity, a novel approach which doubles compute throughput for deep neural networks.

Sparsity is possible in deep learning because the importance of individual weights evolves during the learning process, and by the end of network training, only a subset of weights have acquired a meaningful purpose in determining the learned output. The remaining weights are no longer needed.

Fine grained structured sparsity imposes a constraint on the allowed sparsity pattern, making it more efficient for hardware to do the necessary alignment of input operands. NVIDIA engineers have found that because deep learning networks are able to adapt weights during the training process based on training feedback, in general the structure constraint does not impact the accuracy of the trained network for inferencing. This enables inferencing acceleration with sparsity. For training acceleration, sparsity needs to be introduced early in the process to offer a performance benefit, and methodologies for training acceleration without accuracy loss are an active research area.

Refer to **Appendix B - Sparse Neural Network Primer** for additional background information on sparsity.

#### Sparse Matrix Definition

Structure is enforced through a new 2:4 sparse matrix definition that allows two non-zero values in every four-entry vector.

A100 supports 2:4 structured sparsity on rows, as shown in Figure 12 below. Due to the well-defined structure of the matrix, it can be compressed efficiently and reduce memory storage and bandwidth by almost 2x.

A100 Fine-Grained Structured Sparsity prunes trained weights with a 2-out-of-4 non-zero pattern, followed by a simple and universal recipe for fine-tuning the non-zero weights. The weights are compressed for a 2x reduction in data footprint and bandwidth, and the A100 Sparse Tensor Core doubles math throughput by skipping the zeros.

Figure 12. A100 Fine-Grained Structured Sparsity

NVIDIA has developed a simple and universal recipe for sparsifying deep neural networks for inference using this 2:4 structured sparsity pattern. The network is first trained using dense weights, then fine-grained structured pruning is applied, and finally the remaining non-zero weights are fine-tuned with additional training steps. This method results in virtually no loss in inferencing accuracy based on evaluation across dozens of networks spanning vision, object detection, segmentation, natural language modeling, and translation.

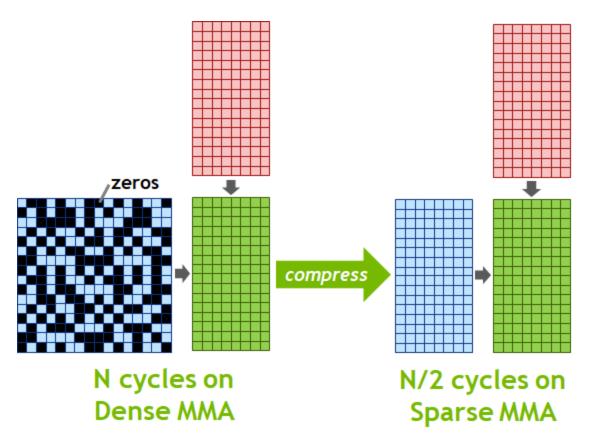

#### Sparse Matrix Multiply-Accumulate (MMA) Operations

A100's new Sparse MMA instructions skip the compute on entries that have zero values, resulting in a doubling of the Tensor Core compute throughput. For example, in Figure 13 Below, Matrix A is a Sparse matrix with 50% sparsity following the required 2:4 structured pattern and Matrix B is a dense matrix of half the size. A standard MMA operation would not skip the zero values and would compute the result for the entire 16x8x16 matrix multiply in N cycles. Using a Sparse MMA instruction, only the elements in each row of Matrix A that have a non-zero value are matched with the corresponding elements from Matrix B. This transforms the computation into a smaller matrix multiply that takes just N/2 cycles, a 2x speedup.

Example Dense MMA and Sparse MMA operations using 16x16 sparse matrix (Matrix A), multiplied by a dense 16x8 matrix (Matrix B). Sparse MMA operation on right doubles throughput by skipping compute of zero values

Figure 13. Example Dense MMA and Sparse MMA operations

#### Combined L1 Data Cache and Shared Memory

First introduced in Volta V100, the NVIDIA combined L1 data cache and shared memory subsystem architecture significantly improves performance, while also simplifying programming and reducing the tuning required to attain at or near-peak application performance. Combining data cache and shared memory functionality into a single memory block provides the best overall performance for both types of memory accesses. The combined capacity of the L1 data cache and shared memory is 192 KB/SM in A100 versus 128 KB/SM in V100.

L1 cache integration within the shared memory block ensures the L1 cache has low latency and high bandwidth. The L1 functions as a high-throughput conduit for streaming data while simultaneously providing high-bandwidth and low-latency access to frequently reused data—the best of both worlds. The A100's larger L1/shared memory subsystem further amplifies performance of applications that use the L1 data cache when accessing device memory, allowing performance levels approaching that of using and explicitly managing fast shared memory. (See the NVIDIA Tesla V100 Whitepaper for examples on how a combined L1 data

cache and shared memory subsystem allows L1 cache operations to attain the benefits of shared memory performance.)

#### Simultaneous Execution of FP32 and INT32 Operations

Similar to Tesla V100 and Turing GPUs, the A100 SM also includes separate FP32 and INT32 cores, allowing simultaneous execution of FP32 and INT32 operations at full throughput, while also increasing instruction issue throughput. Many applications have inner loops that perform pointer arithmetic (integer memory address calculations) combined with floating-point computations that will benefit from simultaneous execution of FP32 and INT32 instructions. Each iteration of a pipelined loop can update addresses (INT32 pointer arithmetic) and load data for the next iteration while simultaneously processing the current iteration in FP32.

#### A100 HBM2 and L2 Cache Memory Architectures

The design of a GPU's memory architecture and hierarchy is critical to application performance, and impacts GPU size, cost, power usage, and programmability. Many different memory subsystems exist in a GPU, from the large complement of off-chip DRAM (frame buffer) device memory, to varying levels and types of on-chip memories, to the register files used in computations in the SM. High-performance HBM2 is the DRAM technology used in the A100 GPU.

The global and local memory areas accessed by CUDA programs reside in HBM2 memory space, and is referred to as device memory in CUDA parlance. Constant memory space resides in device memory and is cached in the constant cache. Texture and surface memory spaces reside in device memory and are cached in texture cache. The L2 cache caches reads from and writes to HBM2 (device) memory. HBM2 and L2 memory spaces are accessible to all SMs and all applications running on the GPU.

#### A100 HBM2 DRAM Subsystem

As HPC, AI, and analytics datasets continue to grow and problems looking for solutions get increasingly complex, more GPU memory capacity and higher memory bandwidth is a necessity. Tesla P100 was the world's first GPU architecture to support the high-bandwidth HBM2 memory technology, while Tesla V100 provided a faster, more efficient, and higher capacity HBM2 implementation. A100 raises the bar yet again on HBM2 performance and capacity.

HBM2 memory is composed of memory stacks located on the same physical package as the GPU, providing substantial power and area savings compared to traditional GDDR5/6 memory designs, allowing more GPUs to be installed in systems. Fundamental details of HBM2 technology are included in our <u>Pascal Architecture Whitepaper</u>.

The A100 GPU includes **40 GB of fast HBM2 DRAM memory** on its SXM4-style circuit board. The memory is organized as five active HBM2 stacks with eight memory dies per stack. With a 1215 MHz (DDR) data rate the A100 HBM2 delivers **1555 GB/sec memory bandwidth**, which is more than 1.7x higher than Tesla V100 memory bandwidth.

#### ECC Memory Resiliency

The A100 HBM2 memory subsystem supports Single-Error Correcting Double-Error Detecting (SECDED) Error Correction Code (ECC) to protect data. ECC provides higher reliability for compute applications that are sensitive to data corruption. It is especially important in large-scale cluster computing environments where GPUs process very large datasets and/or run applications for extended periods. Other key memory structures in A100 are also protected by SECDED ECC including the L2 cache and the L1 caches and register files inside all the SMs.

#### A100 L2 Cache

The A100 GPU in the A100 Tensor Core GPU includes 40 MB of L2 cache, which is 6.7x larger than Tesla V100 L2 cache. The substantial increase in L2 cache size significantly improves performance of many HPC and AI workloads because larger portions of datasets and models can now be cached and repeatedly accessed at much higher speed than reading from and writing to HBM2 memory. Some workloads that are limited by DRAM bandwidth will benefit from the larger L2 cache, such as deep neural networks using small batch sizes.

The A100 L2 cache is divided into two partitions to enable higher bandwidth and lower latency memory access. Each L2 partition localizes and caches data for memory accesses from SMs in the GPCs directly connected to the partition. This structure enables A100 to deliver a 2.3x L2 bandwidth increase over V100. Hardware cache-coherence maintains the CUDA programming model across the full GPU, and applications will automatically leverage the bandwidth and latency benefits of A100's new L2 cache.

L2 cache is a shared resource for the GPCs and SMs and lies outside of the GPCs. The L2 cache is divided into two partitions to enable higher bandwidth and lower latency memory access. Each L2 partition localizes and caches data for memory accesses from SMs in the GPCs directly connected to the partition. This structure enables A100 to deliver a 2.3x L2 bandwidth increase over V100. Hardware cache-coherence maintains the CUDA programming model across the full GPU, and applications will automatically leverage the bandwidth and latency benefits of A100's new L2.

Each L2 cache partition is divided into 40 L2 cache slices. Eight 512 KB L2 slices are associated with each memory controller. As mentioned in the MIG section below, an L2 slice group composed of 10 L2 cache slices is included in each GPU slice in a GPU Instance of a MIG configuration. The A100 L2 read bandwidth is 5120 Bytes/clk, compared to V100 L2 cache read bandwidth of 2048 Bytes/clk.

The NVIDIA Ampere architecture provides L2 cache residency controls for the programmer to manage data to keep or evict from the cache (see the **CUDA Advances for NVIDIA Ampere Architecture GPUs** section below for more details).

The NVIDIA Ampere architecture adds Compute Data Compression to accelerate unstructured sparsity and other compressible data patterns. Compression in L2 provides up to 4x improvement to DRAM read/write bandwidth, up to 4x improvement in L2 read bandwidth, and up to 2x improvement in L2 capacity.

Table 4. Comparison of NVIDIA Data Center GPUs

| GPU Features                                              | NVIDIA Tesla P100 | NVIDIA Tesla V100 | NVIDIA A100          |

|-----------------------------------------------------------|-------------------|-------------------|----------------------|

| GPU Codename                                              | GP100             | GV100             | GA100                |

| GPU Architecture                                          | NVIDIA Pascal     | NVIDIA Volta      | NVIDIA Ampere        |

| GPU Board Form Factor                                     | SXM               | SXM2              | SXM4                 |

| SMs                                                       | 56                | 80                | 108                  |

| TPCs                                                      | 28                | 40                | 54                   |

| FP32 Cores/SM                                             | 64                | 64                | 64                   |

| FP32 Cores/GPU                                            | 3584              | 5120              | 6912                 |

| FP64 Cores/SM (excl. Tensor)                              | 32                | 32                | 32                   |

| FP64 Cores/GPU (excl. Tensor)                             | 1792              | 2560              | 3456                 |

| INT32 Cores/SM                                            | NA                | 64                | 64                   |

| INT32 Cores / GPU                                         | NA                | 5120              | 6912                 |

| Tensor Cores / SM                                         | NA                | 8                 | 42                   |

| Tensor Cores / GPU                                        | NA                | 640               | 432                  |

| GPU Boost Clock                                           | 1480 MHz          | 1530 MHz          | 1410 MHz             |

| Peak FP16 Tensor TFLOPS with FP16 Accumulate <sup>1</sup> | NA                | 125               | 312/6243             |

| Peak FP16 Tensor TFLOPS with FP32 Accumulate <sup>1</sup> | NA                | 125               | 312/6243             |

| Peak BF16 Tensor TFLOPS with FP32 Accumulate <sup>1</sup> | NA                | NA                | 312/624 <sup>3</sup> |

| Peak TF32 Tensor TFLOPS <sup>1</sup>                      | NA                | NA                | 156/312 <sup>3</sup> |

| Peak FP64 Tensor TFLOPS <sup>1</sup>                      | NA                | NA                | 19.5                 |

| Peak INT8 Tensor TOPS <sup>1</sup>                        | NA                | NA                | 624/1248³            |

| Peak INT4 Tensor TOPS <sup>1</sup>                        | NA                | NA                | 1248/2496³           |

| Peak FP16 TFLOPS¹ (non-Tensor)                            | 21.2              | 31.4              | 78                   |

| Peak BF16 TFLOPS¹ (non-Tensor)                            | NA                | NA                | 39                   |

| Peak FP32 TFLOPS¹ (non-Tensor)                            | 10.6              | 15.7              | 19.5                 |

| Peak FP64 TFLOPS¹ (non-Tensor)                            | 5.3               | 7.8               | 9.7                  |

| Peak INT32 TOPS <sup>1</sup>                              | NA                | 15.7              | 19.5                 |

| Texture Units                                             | 224               | 320               | 432                  |

| Memory Interface                                          | 4096-bit HBM2     | 4096-bit HBM2     | 5120-bit HBM2        |

| Memory Size                                               | 16 GB             | 32 GB / 16 GB     | 40 GB                |

| Memory Data Rate                                          | 703 MHz DDR       | 877.5 MHz DDR     | 1215 MHz DDR         |

| Memory Bandwidth                                    | 720 GB/sec    | 900 GB/sec               | 1555 GB/sec                  |

|-----------------------------------------------------|---------------|--------------------------|------------------------------|

| L2 Cache Size                                       | 4096 KB       | 6144 KB                  | 40960 KB                     |

| Shared Memory Size / SM                             | 64 KB         | Configurable up to 96 KB | Configurable up to<br>164 KB |

| Register File Size / SM                             | 256 KB        | 256 KB                   | 256 KB                       |

| Register File Size / GPU                            | 14336 KB      | 20480 KB                 | 27648 KB                     |

| TDP                                                 | 300 Watts     | 300 Watts                | 400 Watts                    |

| Transistors                                         | 15.3 billion  | 21.1 billion             | 54.2 billion                 |

| GPU Die Size                                        | 610 mm²       | 815 mm <sup>2</sup>      | 826 mm2                      |

| TSMC Manufacturing Process                          | 16 nm FinFET+ | 12 nm FFN                | 7 nm N7                      |

| Peak rates are based on     Four Tensor Cores in an |               |                          |                              |

- Four Tensor Cores in an A100 SM have 2x the raw FMA computational power of eight Tensor Cores in a GV100 SM.

- 3. Effective TOPS / TFLOPS using the new Sparsity Feature

**Note:** Because the A100 Tensor Core GPU is designed to be installed in high-performance servers and data center racks to power AI and HPC compute workloads, it does not include display connectors, NVIDIA RT Cores for ray tracing acceleration, or an NVENC encoder.

# Maximizing Tensor Core Performance and Efficiency for Deep Learning Applications

As discussed above, the NVIDIA Tensor Core was first introduced in the NVIDIA Volta GPU architecture to deliver a significant performance speedup for matrix multiplication operations that are common in neural network training and inferencing. Tensor Cores on Volta supported an 8x peak speedup for mixed-precision matrix multiplication compared to standard FP32 precision operations.

Compared to Tesla V100, the NVIDIA Ampere architecture-based A100 GPU has more SMs (108 vs 80) with third-generation Tensor Cores capable of larger Tensor operations. The Tensor Cores in the A100 GPU support peak mixed-precision compute performance that is 16x higher than standard FP32 FMA operations.

Several new features and optimizations were introduced in the NVIDIA Ampere architecture that enhance utilization of the Tensor Cores, improve programmability, reduce software complexity, reduce memory bandwidth usage, and reduce latency and other overheads.

# Strong Scaling Deep Learning Performance

Deep learning requires massive compute resources, but the parallelism is broken up into small sequentially dependent chunks of work. A typical deep neural network consists of long chains of

interconnected layers. Each layer performs an operation similar to General Matrix Multiplication (GEMM) by taking a matrix of input values and multiplying it with a matrix of weights to create an output matrix. The output matrix then typically goes through some activation math before being sent to the next layer of the network. The output matrix of each GEMM is broken down into smaller tiles which map across the multiple SMs in the GPU.

The NVIDIA Ampere architecture targets strong scaling to deliver speedups on existing deep neural networks. Weak scaling is an easier target where the workload parallelism must grow to leverage the faster architecture. With strong scaling the workload per GPU is fixed from one architecture to the next. In the context of deep learning, this means that the GEMM tile size per SM must not grow even while the A100 Tensor Cores consume data 2.5x faster than V100. The NVIDIA Ampere architecture implemented several features and optimizations, described below, to deliver data to the Tensor Cores at a faster rate and more efficiently.

# New NVIDIA Ampere Architecture Features Improved Tensor Core Performance

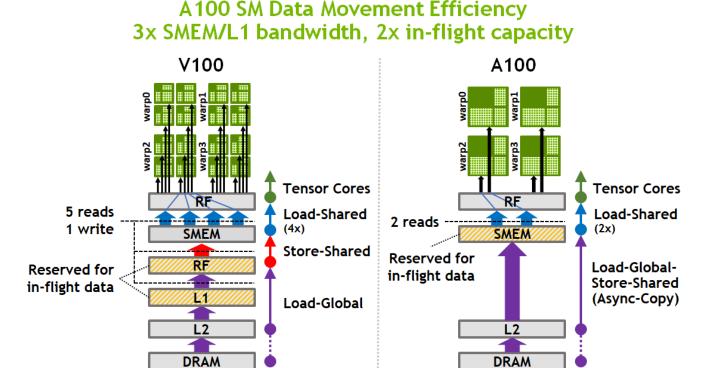

**Data sharing improvements** - The NVIDIA Ampere architecture third-generation Tensor Core allows data to be shared across all 32 threads in a warp, compared to 8 threads on Volta's Tensor Core. Sharing data across more threads reduces the register file bandwidth for feeding data to the Tensor Cores. It also reduces the amount of redundant data loaded into the register files from shared memory (SMEM), which saves both bandwidth and register file storage. To further improve efficiency, A100 Tensor Core instructions increase the k dimension of the matrix multiply per instruction by up to 4x relative to V100. Overall, when computing matrix multiply operations A100 issues 8x fewer instructions and performs 2.9x fewer register file accesses than V100.

### A100 Tensor core: 2x throughput vs. V100, >2x efficiency A100 TC Instruction (2048 MACs, 8 cycles) V100 TC Instruction A100 TC 32-Thread (1024 MACs, 8 cycles) (1 cycle) Operand **FFMA** 8T 8T **8T** 8T Sharing (32 MACs, 2 cycles)

| 16x16x16 matrix multiply     | FFMA | V100 TC | A100 TC | A100 vs.<br>V100<br>(improvement) | A100 vs.<br>FFMA<br>(improvement) |

|------------------------------|------|---------|---------|-----------------------------------|-----------------------------------|

| Thread sharing               | 1    | 8       | 32      | 4x                                | 32x                               |

| Hardware instructions        | 128  | 16      | 2       | 8x                                | 64x                               |

| Register reads+writes (warp) | 512  | 80      | 28      | 2.9x                              | 18x                               |

| Cycles                       | 256  | 32      | 16      | 2x                                | 16x                               |

A100's Tensor Core increases thread sharing by 4x over V100. For a 16x16x16 matrix multiply, A100's enhanced 16x8x16 Tensor Core (TC) instructions improve on V100 by reducing register accesses from 80 to 28, and hardware instructions issued from 16 to 2. Cycle counts are per SM partition. Note: Each V100 8x8x4 TC instruction (CUDA warp-level instruction) is translated into four lower-level MMA hardware instructions.

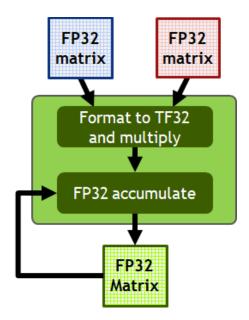

Figure 14. A100 Tensor Core Throughput and Efficiency

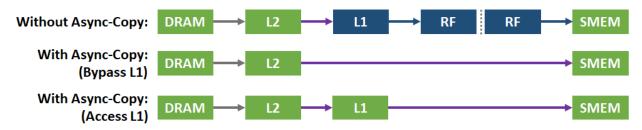

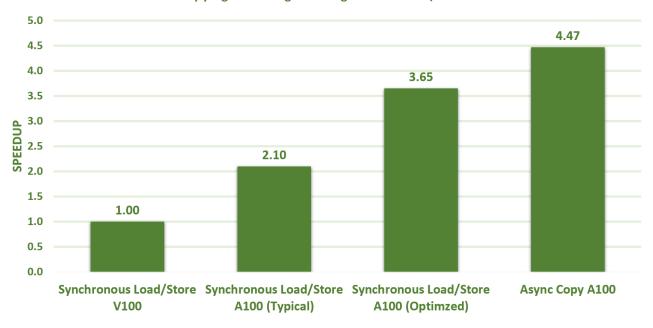

**Data Fetch Improvements** - NVIDIA Ampere architecture includes a new asynchronous copy instruction that loads data directly from global memory (typically from L2 cache and DRAM) into SM shared memory. On Volta, data was first loaded through L1 cache into the register file with load-global instructions, then transferred from the register file to shared memory with store-shared instructions, and finally loaded from shared memory into registers of multiple threads and warps with load-shared instructions. The new load-global-store-shared asynchronous copy instruction in NVIDIA Ampere architecture GPUs saves SM internal bandwidth by avoiding a roundtrip through the register file, and also eliminates the need to allocate register file storage for the in-flight data transfers. More details on the asynchronous copy instruction are provided later in this paper.

32 Threads (Warp)

A100 improves SM bandwidth efficiency with a new load-global-store-shared asynchronous copy instruction that bypasses L1 cache and register file (RF). Additionally, A100's more efficient Tensor Cores reduce shared memory (SMEM) loads.

Figure 15. A100 SM Data Movement Efficiency

New asynchronous barriers work together with the asynchronous copy instruction to enable efficient data fetch pipelines, and A100 increases maximum SMEM allocation per SM 1.7x to 164 KB (vs 96 KB on V100). With these improvements A100 SMs continuously data stream data to keep the L2 cache constantly utilized.

**L2 Cache and DRAM Bandwidth improvements** - The NVIDIA A100 GPU's increased number of SMs and more powerful Tensor Cores in turn increase the required data fetch rates from DRAM and L2 cache. To feed the Tensor Cores, A100 implements a 5-site HBM2 memory subsystem with bandwidth of 1555 GB/sec, over 1.7x faster than V100. A100 further provides 2.3x the L2 cache read bandwidth of V100.

Alongside the raw data bandwidth improvements, A100 improves data fetch efficiency and reduces DRAM bandwidth demand with a 40 MB L2 cache that is almost 7x larger than that of Tesla V100. To fully exploit the L2 capacity A100 includes improved cache management controls. Optimized for neural network training and inferencing as well as general compute workloads, the new controls ensure that data in the cache is used more efficiently by minimizing writebacks to memory and keeping reused data in L2 to reduce redundant DRAM traffic.

For example, for DL inferencing workloads, ping-pong buffers can be persistently cached in the L2 for faster data access, while also avoiding writebacks to DRAM. For producer-consumer chains, such as those found in DL training, L2 cache controls can optimize caching across the write-to-read data dependencies. In LSTM networks, recurrent weights that are shared across multiple GEMM operations can be preferentially cached and reused in L2.

A100 L2 cache residency controls help applications reduce DRAM bandwidth. This example shows different data buffers highlighted with colors to indicate data that has been marked for persistent caching in L2.

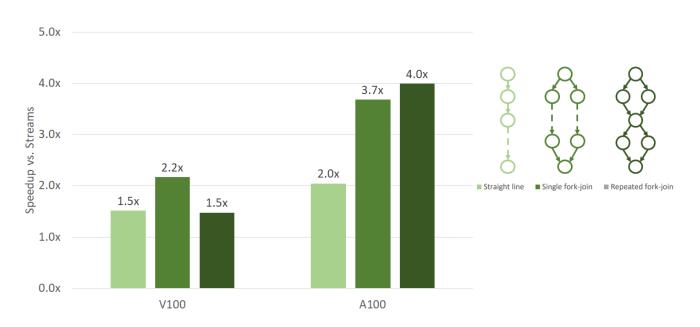

Figure 16. A100 L2 cache residency controls